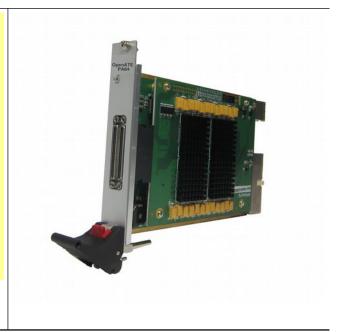

## **OpenATE PA64IX**

#### **3U PXI Low Voltage Dynamic Digital PE Card**

64 input / output channels, with static configuration

- 32 M of on-board vector memory per channel

- -0.5 ~ +3.5V VIH VIL per channel

VTH per channels

- 33 MHz data rate

- 32M capture log memory

- Operates as a stand-alone card or with up to 16 boards in parallel.

- API & Pattern Editor

#### Description

The PA64IX represents a new level of performance and capabilities for PXI-based digital instrumentation. Each card can function as a stand-alone digital subsystem or if required, multiple cards can be interconnected, supporting up to 1024 bi-directional pins (16 boards). The PA64IX also supports deep pattern memory by offering 32 M of on-board vector memory with static per pin direction control and with test rates up to 33 MHz.

With new 32M capture memory, PA64IX can capture 64 channels data log .

#### Features

The PA64IX supports -0.5  $\sim$  +3.5 VTH per channel ,VIH/VIL per channel.

The PA64IX offers 1, 2 driver TG Edges, 1 strobe TG Edges, and four drive data formats are supported: RTZ (Return To Zero),

RTO (Return To One), NRZ (Non Return To Zero), SBC (Surround By Complement) which can providing flexibility to create a variety of bus cycles and waveforms to test board and box level products

#### Compatibility

All OpenATE Interfaces PXI cards comply with the PXI Specification 2.0 (issued Aug. 2000)

#### Software

The PA64 is supplied with API and Pattern Editor. Pattern Editor is a software tool that edits test patterns.

#### Application

- Digital Pattern Capture

- Digital Pattern Generation

- Hybrid and Digital IC Testing

### **OpenATE** Inc.

The Open Solution for IC Tester

Copyright © OpenATE Inc., All rights reserved. Specifications subject to change without notice.

# **OpenATE PA64IX**

### Specifications

| Pin Electronics                                        |                           | Logic Sequencer                                                                              |                                              |

|--------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|

| I/O Channels                                           | 64, per board resource    | Pattern Symbols                                                                              | 0, 1                                         |

| Test rate                                              | 33MHz                     | LMSYNC to PXI<br>Trigger Bus                                                                 | For Sync With other<br>Instruments           |

| Input Level (Vih/ Vil)                                 | -0.5 ~ +3.5V per channel  | Ignore Fail By LM<br>Address                                                                 | YES                                          |

| Output Level (Vth)                                     | -0.5 ~ +3.5V per channels | Vector Memory                                                                                | 32M(length) × 64(channels)                   |

| Output Impedance                                       | 50 Ohm                    | Log Memory                                                                                   | 32M for capture log                          |

| • Timing                                               |                           | • Trigger                                                                                    |                                              |

| Period Resolution                                      | 10nS                      | PXI_TRIG Bus                                                                                 | 8                                            |

| Pin TG Edge Resolution                                 | 10nS                      | Physical Properties                                                                          |                                              |

| Minimum Pulse Width                                    | 10nS                      | Bus Interface                                                                                | PXI                                          |

| Driver TG Edges                                        | 2, per pin resource       | Dimensions                                                                                   | 3U                                           |

| Strobe TG Edges                                        | 1, per pin resource       | Power Requirements                                                                           | 3.3V@3A, 5V@3A<br>12V@1A                     |

| • Formater                                             |                           | System Clock                                                                                 | 100MHz                                       |

| Format Sets                                            | 1                         | Bus & Signals                                                                                | 8 PXI Trigger bus lines for<br>parallel test |

| RTZ, Return To Zero<br>RTO, Return To One              |                           |                                                                                              |                                              |

| NRZ, Non Return To Zero<br>SBC, Surround By Complement |                           | • Software                                                                                   |                                              |

| Environmental                                          |                           | Maximum boards in one system                                                                 | 16                                           |

| Operating Temperature                                  | 0 ~ 50° <b>℃</b>          | PXI Compliance                                                                               |                                              |

| Storage Temperature                                    | -20 ~ 70 <b>°C</b>        | All OpenATE Interfaces PXI cards comply with the<br>PXI Specification 2.0 (issued Aug, 2000) |                                              |

**OpenATE Inc.**

The Open Solution for IC Tester

Copyright © OpenATE Inc., All rights reserved. Specifications subject to change without notice.